Új hozzászólás Aktív témák

-

Petykemano

veterán

MLiD infoi szerint Strix Halo néven jön a mega APU (40CU)

Sajnos nem budget gaming, hanem prémium mobile. 16 mag. Chiplet. Szerintem a 16 mag sok, de Végülis ha csak az IOD nagyobb, akkor lehet ilyen is, olyan is.Találgatunk, aztán majd úgyis kiderül..

-

Petykemano

veterán

AdoredTV - Zen5 [link]

újdonságként ható információk:

- kétirányú gyűrű helyett létra topológia a magok közötti kommunikáciban.

- 2MB valamint 3MB L2$-sel rendelkező ES példányok. (Ennek jelentősége persze csak MT workload alatt van)Találgatunk, aztán majd úgyis kiderül..

-

Petykemano

veterán

válasz

S_x96x_S

#8728

üzenetére

S_x96x_S

#8728

üzenetére

Wow

Vajon mi készül majd ott?

Kis monolitikus GPU? APU? Base die? Cache die? Zen5c?A Samsung gyártástechnológia híres arról, hogy az energiahatékonysága magasabb frekvenciákon és az Fmax is rosszabb. Elméletileg ahhoz lehet alkalmas, ahol legfontosabb szempont a sűrűség és nem szempont a magas frekvencia és nem olyan részegység, ahol nagy fogyasztás történne.

Találgatunk, aztán majd úgyis kiderül..

-

Petykemano

veterán

A számok első ránézésre nem tűnnek olyan rossznak.

De valójában a visszaesés az AMD-nél is érezhető.

Nem tudom pontosan melyik hónaptól írják az AMD-hez jóvá a Xilinx bevételeit, gyanítom, hogy kb 2022Q1-től indulhatott.

Mindenesetre ha a 2023Q1-ből azt kivonod, akkor válik láthatóvá, hogy ahhoz az időszakhoz képest mekkora visszaesés van a Client computing divíziónál.

A grafikai divíziónál is a PS5-re való nagy kereslet fedi el a GPU-k iránti kereslet-visszaesést.Persze hát végső soron ezek mind a vállalat részei.

Találgatunk, aztán majd úgyis kiderül..

-

Petykemano

veterán

Állítólag a MSFT partnerségbe lépett / segít / rendelt semi custom AI chip tervezést az AMD-től/vel

[link]Találgatunk, aztán majd úgyis kiderül..

-

Petykemano

veterán

Kijött egy új video MLiD-től.

Új info az eddigiek felett talán nem is jelent meg az architektúráról.

Az került megerősítésre, hogy az IPC növekedést elsősorban nem cache méretek növelésével érik el, hanem architekturális változtatásokkal. Ennek megfelelően csak az L1$ mérete változik. Feltehetőleg szélesedik az architektúra. Ez alapján talán nem a valóságtól elrugaszkodott a következő szerepleosztást felfételezni, hogy minek miben van szerepe, mire van nagyobb hatással:L1$ => az architektúra szélességével függ leginkább össze - az Instruction Level parallelism (ILP)-re lehet hatással, pontosabban egy szélessebb architektúra kiszolgálásához értelemszerűen nagyobb cache szükséges. Azonos architektúra szélességet feltételezve a mérete sokkal kevésbé lehet hatással az IPC-re, mint a késleltetés.

L2$ => Feltételezve azt, hogy egy meghatározott architektúra szélesség esetén egy programszál meghatározó adataianak fontos része az L1$-ben, meghatározó része pedig a már 1MB-os L2$-ben elfér, az L2$ további növelése csak a - az SMT miatt - a multithreading teljesíményre lehet hatással.

Azonban az architektúra szélesedése nyomást gyakorolhat az L2$-re is. Szélesedő architektúra mellett változatlan L2$ méret esetleg csökkentheti a - az SMT-vel nyújtott - multithreading teljesítménytL3$ => ez már egyértelműen a magok között megosztható adatokról szól. Bizonyos méret felett már szinte semmilyen hatást nem tud gyakorolni a ST teljesítményre (különösen nem victim viselkedésű cache esetén) És össze nem függő MT programszálak esetén is valószínűleg kicsi a jelentősége. Értelemszerűen összefüggő, adatokat egymás között megosztó, közösen használó programszálak esetén is érvényes a csökkenő határhatékonyság elve.

Mindezzel együtt számomra a legmeglepőbb mégis az, hogy nem szerepelt a roadmap-en az elkövetkező szerverplatform-X esetén a 3D stackelt L3$ rétegek számának emelése.

(Egyébként az is érdekes, hogy lehet, hogy a Zen5c szerver N3-on előbb fog debütálni, mint a Zen5 szerver N4-en.)

Találgatunk, aztán majd úgyis kiderül..

-

Petykemano

veterán

Megjelent egy video az Ampere One-ról, amin egy lapkát mutogattak [link]

1 központi Compute Die - 192 maggal, N5-ön

2db IO Die.Mivel a szerverpiacon a 4GHz feletti frekvencia, amit az asztali cpuk elérnek, gxakorlatilag nem létezik, így a ST teljesítmény, a fogyasztás és a magszám elég versenyképes lehet.

Talán kicsit kezd szorítani az idő a zen4c kihozatalára.(És hogy idén év végén mozgolódni kezdjenek a zen5-tel)

Az idő talán ott is kezd szorítani, hogy már ez is chiplet. Persze nem pont olyan, mint az AMD megoldása, ami első ránézésre lényeges előnyben van a skálázhatóság tekintetében, de az chipletezés lassan előnyből iparági standarddé olvad.

Találgatunk, aztán majd úgyis kiderül..

-

Petykemano

veterán

válasz

Alogonomus

#8762

üzenetére

Alogonomus

#8762

üzenetére

Érdekes. Én épp fordítva látom.

Én nem tartom magam Arm drukkernek. Szerintem az ARM energiahatékonyságbeli előnye nem magától értetődő. Nem mondom, hogy negligálható, de szerintem tervezési okokra visszavezethető: úgy vélem, hogy az a megközelítés, amit az AMD és az Intel használ a 5-6GHz-ek elérése érdekében mind a lapkaméretre, mind pedig a 3-4Ghz-es amúgy hatékony sávbeli fogyasztásra is negatív hatással lehet.

Az bizonyos, hogy ARM alapon is lehet versenyképes processzort tervezni. Talán kijelenthető, hogy az épp vezető (Intel vagy AMD) X86 megoldáshoz képest teljesítményben általában egy generációnyira le van maradva, ugyanakkor - fentieknek megfelelően - általában nincs lemaradva gyártástechnológiában, részben ennélfogva kisebb lapkából készül és nagyonis versenyképes fogyasztással. Nyers számok alapján a bemutatott termékek számomra versenyképesnek tűnnek.

Ahogy mondod, az AMD 4 generáció óta ostromolja, küszködik a szerverpiacon való nagyob piaci részesedés elérésével. Eközben többször is volt már több szempontból jobb, de legalábbis nagyon versenyképes és kompatiblis termékük, mint a piacvezető Intelnek és idénre jósolják azt, hogy elérheti a 20%-os piaci részesedést . Mindeközben az ARM az események (az Intellelassulása) farvizén evezve olyan termékekkel, amelyekért az AMD-t kiröhögte és lesajnálta (volna) a közönség (sok, de gyengébb mag, energiahatékonyabb socket), mondhatnám különösebb megerőltetés, küszködés nélkül, szélárnyékban értek el az AMD-éhez képest 2/5-ös részesedést, miközben a megoldás használatához ahogy mondtad is, túl kell lépni a kompatibilitási kérdéseken is.

Ebben természetesen nyilván benne vannak nem csak az Ampere termékei, hanem az Amazon Gravitonm, Nvidia és esetleg más in-house fejlesztések is.

Nem állítom, hogy a kompatibilitási kérdés ne okozhatna valahol egy üvegplafont az ARM terjedésének. Elképzelhető, hogy van egy bizonyos százalék, ameddig tartanak a vállalkozókedvű, agilis cégek, és a nagy tömeg, amelyik még ma is intelt vesz, egyszerűen annyira mamut, hogy csak rendkívül nehezen állna át.

De az, hogy ennyire észrevétlenül növekszik engem nem annyira magabiztosággal (x86-biztossággal) tölt el, hanem inkább aggaszt.

Különösen akkor van ok (az x86-osoknak) aggódni, ha igaz az, hogy minden fejlesztő olyan szerveres környezetet preferál, amin fejleszt és ha a fejlesztők körében terjed az Apple M1-M2. Többek között ezért is fontos, hogy ne totojázzon az AMD a Zen5-tel. Ugyanis az Apple hamarosan előállhat az N3-on készülő új megoldásával M3-mal és a pletykák szerint az Apple is készül szerverlapkákkal, amit lehet, hogy eleinte belső használatra készítenek, de ha a cloud az új nagy piac, akkor miért ne haraphatnának bele a szerver/cloud piacba saját gyártású hardverrel, hovatovább szerverrel (hardver+szoftver)?

Találgatunk, aztán majd úgyis kiderül..

-

Petykemano

veterán

"According to several sources, Intel could buy Ampere Computing. At the moment, however, the price of the young company seems to be too high."

[link]Találgatunk, aztán majd úgyis kiderül..

-

Petykemano

veterán

válasz

Petykemano

#8761

üzenetére

Petykemano

#8761

üzenetére

Érdekes elemzés az AmpereOne A192-ről [link]

Kritizálja a teljesítmény mutatókat

Pl hogy a core/rack, amiben 3x értéket mutatnak fel, semmit nem mond a tejesítményről.

És a stable diffusiom teszt konfigurációja is sajátos.[ Szerkesztve ]

Találgatunk, aztán majd úgyis kiderül..

-

Petykemano

veterán

AdoredTV-nek volt a napokban egy videója a a Mi300-ról, pontosabban azok variánsairól.

Természetesen csak erős idegzetűek nézzék meg. Akik képtelenek feldolgozni egy még meg nem jelent termékről szóló műsorban található pontatlanságokat, az inkább tartózkódjon ettől és várja meg a hivatalos termékbejelentéstA köztudatban eddig 1-2 Mi300 variánsról tudtunk.

- volt egy, ami 6db GPU és 3db CPU chipletet tartalmaz

- ez alapján feltételezhető volt, hogy létezhet olyan verzió is, amiben nincs CPU, csak 8db GPU chiplet.Nem meglepő módon AdoredTV videójában felvillant az a lehetőség is, hogy 9db CPU chiplet és 2db GPU kerüljön összetokozásra.

De miért ne lehetne 12db CPU chiplet összetokozva - GPU nélkül? Tulajdonképpen a megrendelő eldöntheti, hogy milyen célre milyen kombinációt szeretne összerakatni.Mindenesetre az elég kemény lenne.

V-cache a CPU chipleten, alatta a bázis lapkákon található infinity cache, amit miért ne használhatna a CPU is (L4$?), és ezt veszi körül a HBM3.Ez persze nyilván nem jelentene minden szoftver számára azonnal gyorsulást, de komoly kihívója lehet a HBM-mel szerelt Sapphire Rapids-nak és a Fugakunak vagy hozzá hasonlóknak.

Találgatunk, aztán majd úgyis kiderül..

-

Petykemano

veterán

válasz

Busterftw

#8777

üzenetére

Busterftw

#8777

üzenetére

Szerintem az AMD tervei ebből a szempontból jobb helyzetbe hozzák néhány éves távlatban.

a P és E magok együttes használatában kulcstényező, hogy milyen cache köti össze őket. Jelenleg az AMD-nél a chipleteket nem köti össze semmi, memórián keresztül tudnak adatot cserélni. Az Intelnél az E és P magok osztoznak a L3$ ring buszán, de kétlem, hogy ezt 8 cluster esetén is még megtehetik, viszont a Meteor lake elvileg egy nagy cache bázislapkával készül. Gondolom az szolgál majd adatmegosztási célokat. Ez amúgy jól hangzik.

Viszont az AMD-nél elvileg az a terv, hogy a létra topológiával megoldják, hogy 16 P mag kerüljön egy lapkára.Pontosítok: Ha ez így lesz, hogy létra topológiával 16 P mag is kerül egy chipletre (L3$ kiemelve, default 3D stacked) akkor az kedvezőbb helyzetbe hozza szerintem az AMD-t, mintha 8 magos maradna a chiplet 8 / 16 magos P/E chipleteket valami cache bázislapka (L4$) kötné össze. Mindazonáltal az is hasznos lenne, a kettő nem feltétlenül zárja ki egymást.

Találgatunk, aztán majd úgyis kiderül..

-

Petykemano

veterán

válasz

S_x96x_S

#8778

üzenetére

S_x96x_S

#8778

üzenetére

> de az extrém nagy MT -re mi lesz az AMD válasza?

Ez költői kérdés, ugye?

Természetesen a ZenXc magok jelentik a választ.Az Arrow Lake-et MLiD 2024Q4-re tette.

Azt tudni véljük, hogy a Zen5 2024Q1-ben is kiadásra kerülhet. Ha valóban csupán egy új core design N4-en, akkor ennek nem hiszem, hogy különösebb akadálya lenne.

2024Q4-re simán megjelenhet desktopon egy 8P + 16E magos Zen5+Zen5c változat.

Ha ez esetleg nem elég, akkor az a kérdés merül föl, hogy vajon a Zen5-re vagy Zen5c chipletre helyezzék-e fel a v-cache-t, amit az dönt el, hogy a Zen5c kap-e TSV-t és/vagy hogy a Zen5c design a magasabb sűrűség miatt nagyobb frekvencia/feszültség regressziót szenved-e el, mint amennyit az eddigi tapasztalatok szerint a V-cache használata megkövetel. Ha ugyanúgy 500-700Mhz-ről kell csak lemondani, akkor elég egyértelmű.Találgatunk, aztán majd úgyis kiderül..

-

Petykemano

veterán

Zen5 spotted? [link]

Találgatunk, aztán majd úgyis kiderül..

-

Petykemano

veterán

válasz

Petykemano

#8806

üzenetére

Petykemano

#8806

üzenetére

Zen5 első bench leak ES engineering sample

Szokásom visszanézni, hogy mikor volt az előző esetben az első leak és ahhoz képest mennyi idő telt el a megjelenésig.

Úgy láttam, hogy a Zen4-ről 2022 májusban érkeztek az első kiszivárgó mérések.

Ehhez képest szeptember végén jelent meg. Az mindössze 4 hónap.Persze azt tudjuk, hogy a Zen4 szándékosan késleltetett design volt, tehát elképzelhető, hogy több felkészülési idő volt és így gyorsabban tudták intézni.

Mindenesetre ez akkor is előrevetíthet akár egy idén év végi Zen5 rajtot.

Persze elképzelhető, hogy tévedek és már május előtt lehetett látni Zen4 ES-t.

A 2024Q1 akkor is reális.[ Szerkesztve ]

Találgatunk, aztán majd úgyis kiderül..

-

Petykemano

veterán

válasz

S_x96x_S

#8810

üzenetére

S_x96x_S

#8810

üzenetére

lelkesítő, de sajnos szerintem valószínűbb, hogy a doboz jobb szélén levő [PROD] feliratnál van a tényleges megjelenés.

Jó lenne tudni, hogy pontosan mit jelképeznek a dobozok. Ha tippelnem kéne, akkor szerintem ez nem az aktív gyártás időszaka, nyilvánvalóan nem is fejlesztésé, hanem inkább valamilyen piacravezetési időszak.

Ne felejtsük el, hogy ez egy DC roadmap, az asztali Raphael nem szerepel rajta, csak sejthető, hogy amikortól tömegtermelésbe kerül a Genoa, akkortól van selejt a Raphael-hez.

Mindazonáltal én azt érzékelem, hogy a Genoa, Genoa-X és Bergamo terjedése is lényegesen lassabban megy végbe, mint a Milané.Viszont ha igazam van, akkor a Zen5 DC termékek 2024Q2-Q3-ban érkeznek. És ha ezek selejtje kerül desktopra, akkor az miért kerülne a boltokba hamarább? Viszont az sem gyakori, hogy 1-1.5 évvel korábban jelenne meg ES bench leak.

Találgatunk, aztán majd úgyis kiderül..

-

Petykemano

veterán

Zen4 Threadripper listed [link]

Találgatunk, aztán majd úgyis kiderül..

-

Petykemano

veterán

Nocsak, talán mégis lesz 5600X3D?

[link]Találgatunk, aztán majd úgyis kiderül..

-

Petykemano

veterán

válasz

S_x96x_S

#8826

üzenetére

S_x96x_S

#8826

üzenetére

Én is olvastam az elemzés nyilvános részét.

Ezt idézném:

"All variants of MI300 start with the same base building block known as the AID, active interposer die. This is a chiplet called Elk Range and is ~370mm2 in size manufactured on TSMC’s N6 process technology. The chip houses 2 HBM memory controllers, 64MB of Memory Attached Last Level (MALL) Infinity Cache, 3 of the latest generation video decode engines, 36 lanes of xGMI/PCIe/CXL, as well as AMD’s network on chip (NOC). In a 4 tile configuration, that is 256MB of MALL Cache vs H100’s 50MB."Számomra meglepő volt, hogy egy ilyen meglehetősen nagynak mondható - 370mm2-es - lapkán a 2HBM vezérlő és az IO mellett csupán 64MB cache fér bele. Elképzelhető, hogy mindezen IO mellett ez a 64MB nem csupán ~35-40mm2, hanem annál több helyet foglal. Mindenesetre egy ekkora lapkában én szeletenként 256MB-ra számítottam.

Mindenesetre végre látjuk akció közben az active interposer-t, amit már régóta vártunk.

Ahhoz képest, hogy milyen kevés az AID-be rejtet cache és mégis milyen nagy a bázislapka, maguk a compute chipletek egészen törpék. A 370mm2-re csupán 210-230mm2-nyi compute lapka kerül.

Kiváncsi vagyok, hogy akár GPU-k terén, akár CPU-k terén ezt a technológiát bevetik-e következő generációk valamelyikében

Ez a CPU-k terén ugye azt jelentené, hogy az IOD bekerül alulra. Kicsit talán növelni kell a méretén, de jelenleg úgysem tartalmaz cache-t. Ha tartalmazna, akkor túl azon, hogy a 2pJ/bit adatátviteli energiahatékonyságon tudnának jelentősen javítani, hanem a chipletek közötti kommunikáció/adatmegosztás meg megoldódna.Ez a megközelítés egyedül a skálázhatóságot rontaná. jelenleg nyugodtan kihagyható egy-egy chiplet, viszont 3D stackelve a hiányzó chipleteket valamilyen strukturális szilíciummal kellene pótolni.

Természetesen én is azt gondolom, hogy anyagköltségben a Mi300 nagyon drága, viszont nem biztos, hogy a 3D stackelés önmagában annyira költséges már, ha beleférhet egy $200-os 5600X3D.

A szóbeszéd szerint azért mégis a konzumer piacon valószínűbb valamilyen infinity fan-out bridge szerű technológia használata.Találgatunk, aztán majd úgyis kiderül..

-

Petykemano

veterán

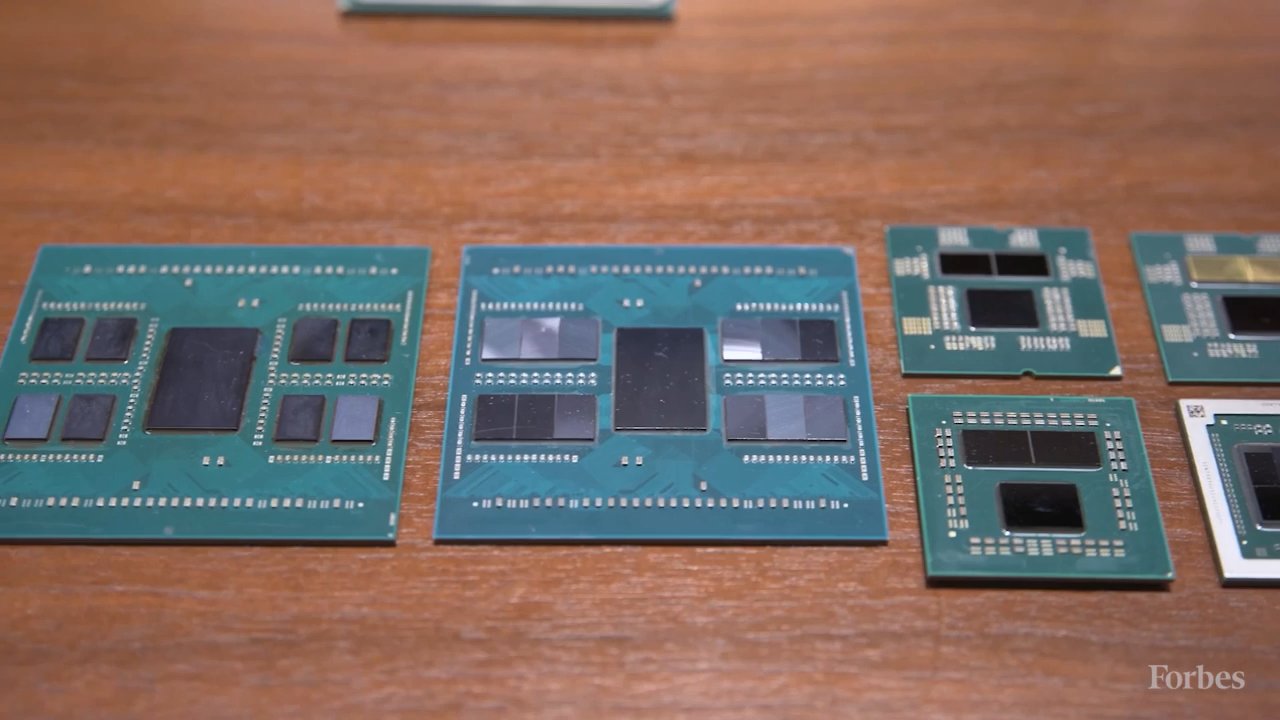

Az ott elvileg balra egy Bergamo lapka.

A kisebb csomagok azonosítását én meg sem kísérlem.Találgatunk, aztán majd úgyis kiderül..

-

Petykemano

veterán

Bergamo spec test

[link]

Meglep, hogy a SpecPower érték az Ampere termékhez képest is milyen jó.Találgatunk, aztán majd úgyis kiderül..

-

Petykemano

veterán

Egyelőre csak érdekességképp osztom meg. Relevanciája abban lehet, hogy nemrégiben felröppent hír, hogy az AMD puhatolózott a Samsung irányába.

"Samsung develops embedded MRAM technology compatible with 14nm FinFET logic" [link]

"He reported that the development level is close to the mass production level by prototyping a 128Mbit large capacity MRAM macro, and showed that the developed eMRAM technology can be applied to even finer 8nm generation FinFET logic."

"The cell area of the prototype eMRAM macro is 0.0242 square μm, which is the smallest eMRAM so far."

"The write pulse width is 200 ns (temperature 160° C.), and the read pulse width is 15 ns (shortest 11 ns, temperature 160° C.)."

"Photo of silicon die of prototype 16Mbit eMRAM macro. The die dimensions have not been announced (assuming the memory density is 18.1Mbit/square mm, which is the same as the 128Mbit macro, the die area is 0.88 square mm)"

Vagyis valamilyen Samsung 14nm-es eljáráson 2.27MB/mm2.

Ez 8nm-en a sűrűség/egységnyi területre vetített kapacitás ennek akár másfélszerese is lehet majd [link]

(Persze azt nem tudjuk, hogy az eMRAM skálázódása is megáll-e valamilyen eljárásnál)TSMC N7-en gyártva a Navi21 esetén az SRAM cellákból álló infinity cache esetén 64MB 40mm2 [link]

Ez 1.6MB/mm2Ezen valamit javít a Zen processzorokhoz alkalmazott 3D V-cache, ami szintén TSMC N7-en 64MB ~36mm2, vagyis ~1.8MB/mm2 (ebbe persze benne van a TSV is, tehát valamivel jobb)

Az MRAM további előnyei azon kívül, hogy kisebb cellaméret szükséges hozzá elvileg az, hogy nem volatilis, nem szivárog, nem fogyaszt sokat, és azért elég gyors is.

Persze az MRAM (STT_MRAM) már készülődik a hatalomátvételre legalább vagy 5-10 éve. Most, hogy a 3D stacking realitássá vált és láthatólag új lendületet vett a számolóegységek cache-sel való kitömése, és 5nm-nél már valószínűleg tényleg elég kicsi lehet az SRAM cellák méretének skálázódása (vagyis nem lesz kisebb a cache kiterjedésének mérete) kiváncsi vagyok, hogy valaki hozzányúl-e.

[ Szerkesztve ]

Találgatunk, aztán majd úgyis kiderül..

-

Petykemano

veterán

Nő már az uborka...

Azon gondolkodtam el, hogy vajon.... mármint én azt érzékelem, hogy a Milanhoz képest a Genoa sokkal lassabban terjed.

Vajon ennek az lehet az oka, hogy volt valami hiba? Vagy ilyen szinten ment rá mindenki szerverkapacitások bővítése és/vagy energiahatékonnyá tétele helyett az AI-ra? Vagy a nagyobb szolgáltatók valójában a Bergamora vártak/várnak?Találgatunk, aztán majd úgyis kiderül..

-

Petykemano

veterán

PHX2 (Little Phoenix): 137mm2

[link]Elvileg ez hybrid

Találgatunk, aztán majd úgyis kiderül..

-

Petykemano

veterán

5600X3D

$229

2023 július 7

Micro Center Only

[link][ Szerkesztve ]

Találgatunk, aztán majd úgyis kiderül..

-

Petykemano

veterán

Találgatunk, aztán majd úgyis kiderül..

-

Petykemano

veterán

Genoa-X sku-k [link]

Találgatunk, aztán majd úgyis kiderül..

-

Petykemano

veterán

AMD GFX1150/1151, the GPUs for Ryzen 8000 “Strix” series

LLVM Zen5

[link]Találgatunk, aztán majd úgyis kiderül..

-

Petykemano

veterán

-

Petykemano

veterán

Találgatunk, aztán majd úgyis kiderül..

-

Petykemano

veterán

válasz

Petykemano

#8849

üzenetére

Petykemano

#8849

üzenetére

Azt hiszem, ez nem mót vég.

A 12-core AMD Ryzen 8050 Zen5 “Strix Point” APU has been spotted

- benchleaks, milkyway, boinc

- AMD Eng Sample: 100-000000994-03_N [Family 26 Model 32 Stepping 0]Korábbi mérnöki példányok felbukkanási ideje alapján tényleg azt lehet jósolni, hogy 7-8 hónap múlva megjelenhet.

Különös, hogy ezúttal az APU változat (mérnöki példánya) látott előbb napvilágot és nem pedig az asztali.Szerintem 4P+8d lehet a hatékony felállás. Azt gondolom, hogy ha már 4 magnál többet kell használni mobil környezetben, akkor ott már nem nagyon lehet korlátozó tényező az, hogy egy d mag esetleg nem megy feljebb 3.5-4Ghz-nél.

mindazonáltal számomra a 40CU-s változat sokkal izgalmasabban hangzik.

Ugyanakkor én korlátozásként (kitolásként) élném meg, ha azt csupán valamilyen előregyártott kompakt egybegépként lehetne megvásárolni. Fájna a szívem, ha a már meglevő kiegészítőimtől (pl CPU hűtő) ezért kéne megválni.[ Szerkesztve ]

Találgatunk, aztán majd úgyis kiderül..

-

Petykemano

veterán

válasz

S_x96x_S

#8857

üzenetére

S_x96x_S

#8857

üzenetére

> én ezt már nem tartom furcsának.

Nem úgy értettem, hogy az APU notebook vagy desktop változata, hanem hogy a Zen5 APU vagy desktop (vagyis chipletes) változata> És az is lehet, hogy csak konzol csip lesz

> .. és nem is kerül kisker forgalomba még egy jó ideig.

Én is ettől tartok.

Nem mintha egyébként megoldhatatlan lenne.

Különösen abban az esetben, ha esetleg ez a változat már nem is monolitikus. Abban esetben akár megoldható lenne, hogy az IO lapka cserélhető.

Milyen szép is volna, ha cserélhető lenne, hogy LPDDR5X vagy DDR5, de több infinity cache. (akár 3D stackelve)Találgatunk, aztán majd úgyis kiderül..

-

Petykemano

veterán

válasz

S_x96x_S

#8864

üzenetére

S_x96x_S

#8864

üzenetére

Különös.

Nem töketes driverrel ki szokták adni. Vajon ennyire fontos, hogy a Phoenix jó benyomást keltsen, hogy csúszhat is, vagy annyira elvonták a szoftveres tagokat a ROCm-hoz, hogy a gpu drivert már nem volt ki fejlessze (RDNA3 esetén látszólag hiányzik a dual issue támogatása és volt egy féléves.időszak az RDNA3 megjelenését követően, amikor RDNA2-től lefelé nem jött driver update ), hogy egyszerűen nem volt ki beletegye az apu támogatását?

Vagy a hardver volt hibás, ahogy a gpu-ról is beszélték, csak erre rászánták a fél éves respint a korrekció érdekében.Találgatunk, aztán majd úgyis kiderül..

-

Petykemano

veterán

Találgatunk, aztán majd úgyis kiderül..

-

Petykemano

veterán

A napokban Lisa Su - a média szerint - cáfolta, hogy az AMD lepaktált volna a Samsunggal. Lisa Su arra hivatkozott, hogy a TSMC nagyon fontos partnerük, hiszen a Mi300 ma nem lenne lehetséges a TSMC nélkül.

Mai Xeet:

"AMD will use Samsung GAAFET nodes."

[link]Természetesen a dolog nem arról szól, hogy az AMD teljesen elhagyja a TSMC-t.

Lehet, hogy csupán arról van szó, hogy összetett chipekhez bizonyos chipletek, vagy kisebb monolitikus mobil chipek és/vagy Xilinx termékek készülnek majd a Samsungnál.[ Szerkesztve ]

Találgatunk, aztán majd úgyis kiderül..

-

Petykemano

veterán

Találgatunk, aztán majd úgyis kiderül..

-

-

Petykemano

veterán

válasz

Petykemano

#8878

üzenetére

Petykemano

#8878

üzenetére

Ez max 24GB, 1.2TB/s

24GB szerintem egy gépnek ma már nem számít kifejezetten soknak. Minimumnak talán inkább a 16GB-ot mondanám. Figyelembe véve, hogy a ebből kellene kiszoglálni az IGP-t is, a 24GB indokolt.

Azon gondolkodtam el, hogy vajon minek kellene teljesülnie, vagy milyen akadályok vannak még ma is az előtt, hogy egy HBM-es készülék készüljön.

Az előny ott van:

- 1.2TB/s, ami egy 150W TDP-be beférő közepes GPU-t taralmazó APU-t

- kompakt módon ki tudna szolgálni.Mit jelent a kompakt (a gép méretén kívül)? Azt, hogy az IOD-ból elhagyható lenne

- a RAM vezérlő, az alaplapról a RAM huzalozás

- a PCIe sávok nagyobb része.Hátránya persze ezzel az volna, hogy sem RAM, sem bővítókártyás GPU fogadására nem volna alkalmas. Nem mintha ezt meg tudnád tenni a manapság egyre népszerűbb kézikonzolok esetén.

A RAM bővítés esetleg lehet szempont. Erre a jövőben viszont talán elegendő lehet PCIe sávokat meghagyni és hagyatkozni a CXL-re, amely esetben egy m.2 csatlakozós bővítőkártya (akár DRAM-okkal) csak overflow kezelését célozná.Ma már nem szükségszerű a nagy interposer, meg tudják oldani "hidakkal". Persze annak is nyilván van valamekkora többletköltsége. Az IOD-on lehet picit spórolni.

Vajon még ennél is olcsóbban megvalósítható LPDDR5X és/vagy 3D stacked v-cache?

Találgatunk, aztán majd úgyis kiderül..

-

Petykemano

veterán

Azt pletykálják, hogy a Strix Point 4P+8e összeállítású lesz ,míg a Strix Halo 8P+8P

Bár mintha valahol azt olvastam volna, hogy 8P+8eUtóbbi nem tűnik túl valószínűnek... kivéve, ha strix halo monolitikus lesz.

Jön a PS5 Pro is.Itt gondolkodtam el, hogy vajon mi lesz végül monolitikus és mi lesz chiplet?

A Strix Point persze valószínűleg monolitikus.

A Strix Halo esetén a 8P+8P egészen úgy hangzik mintha chipletes lenne: 2 hagyományos Zen5 chiplet + egy 40CU-t tartalmazó "IO" lapka. Egy 40CU-s IO lapkát nem volna praktikus úgy tervezni, hogy azt akár diszkrét kártya formájában is el lehessen adni? És akkor vajon a PS5 Pro is ilyen felépítést kap, vagy az marad monolitikus? Ha az monolitikus, akkor lehet-e a Strix Halo is monolitikus inkább?

Találgatunk, aztán majd úgyis kiderül..

-

Petykemano

veterán

Zen5 (Zen 5) benchmarks leak - RedGamingTech

CineBench R23 (MT)

16 Core = 49000

12 Core = 36000

8 Core = 23000

6 Core = 17000Igen különös eredmények. A 16 és 12 magos változat rendre 27% és 23%-os előrelépést mutat. A 8 és 6 magos viszont csak 12%-ot. Ez igencsak meglepő. Azt jelenti, hogy a Zen5 tulajdonképpen relatív sokat fogyaszt és a 12-16 magos változatoknál a nagyobb TDP nagyonis ki van használva.

De ugyanakkor az energiaéhség nem meglepő, ha figyelembe vesszük azt, hogy jelenlegi tudásunk szerint a rendkívül Zen5 N4P gyártástechnológián fog készülni. Ennek megfelelően a target - a Zen3-hoz hasonlóan - a ST (+lightly threaded) teljesítmény növelése lehetett, miközben - a Zen3-hoz hasonlóan - a MT teljesítménybeli növekedése korlátozott. Ez majd az N3_ port esetén korrigálódik. A dense és mobil chip azon fog készülni.

A szöveg alapján a R23 ST mérésben 2500-3000 között teljesít. Ami egy elég tág intervallum. És persze ezt a tág meghatározást már akkor is teljesítik, ha a MT értékeknél látott 23-27%-os növekményt teljesítik.

És persze ne vegyük készpénznek a fent látott számokat.

Találgatunk, aztán majd úgyis kiderül..

-

Petykemano

veterán

Vector Width

Znver1: AVX2 128 bit

Znver2: AVX2 256 bit

Znver3: AVX2 256 bit

Znver4: AVX512 512 bit

Znver5: AVX512 512 bit*2

[link]Találgatunk, aztán majd úgyis kiderül..

-

Petykemano

veterán

válasz

Petykemano

#8907

üzenetére

Petykemano

#8907

üzenetére

Nagyon erősnek tűnik a hype és az elégedettség a zen5 tesztpéldányokkal.

Azt nézegettem, hogy Vajon mikor jelentek meg az első olyan leak-ek, amiket nem Mlid, RGT jelentettek meg, hanem a twitter sejtelmes közönsége is somolyogva lebólogatott. Szerintem nyáron ilyen már biztos történt.

A 2024Q1-es rajt elég valószínű.

Igazából persze a nép annak örülne, ha karácsonyra vihetne haza egyet.A 25% körüli ST teljesítménynövekedés valószínű. Bármi ennél jobb, legyen inkább meglepetés. A raptor lake refresh nem tűnik túl erősnek. Mivel az Intel árat akart volna emelni, ezért az árcsökkentés valószínűtlen, tehát minimum a zen3 borsos árazásához való visszatérés várható. Főleg a kisebb magszámú skuknál.

Találgatunk, aztán majd úgyis kiderül..

-

Petykemano

veterán

válasz

S_x96x_S

#8909

üzenetére

S_x96x_S

#8909

üzenetére

Az egy szerver roadmap.Abból is látszik, hogy nem az asztali megjelenést látjuk, hogy a roadmap szerint a Raphael alapú AM5 platform előkészítése 2023 során zajlik és 2023Q4-ben kerül piacra vezetésre - miközben az asztali Zen4 már 2022 év vége óta elérhető.

Nem állítom persze, hogy mindent 1 évvel elcsúsztatva kell értelmezni, csak azt, hogy amit ezen az ábrán látunk az nem az asztali termék megjelenésére vonatkozóan mérvadó.

Abban sem vagyok biztos, hogy vajon ez a roadmap még pontos. A Bergamo emlékeim szerint például 2 hónapja jelent meg, tehát csúszott 2 negyedévet.

Elnézést, persze én is csak ködszurkálok. Meglátjuk majd.

Két dolog miatt hiszek a 2024Q1-es rajtban:

Egyrészt mert az architektúrák közötti intervallumszámítás alapján - figyelembe véve a Zen4 2 negyedéves csúszását - úgy jön ki.

Másrészt szerintem az üdvrivalgás is korai jelenség volna 1 évvel a kiadást megelőzően.De majd meglátjuk.

Szerintem CES-re remek téma lenne.[ Szerkesztve ]

Találgatunk, aztán majd úgyis kiderül..

-

Petykemano

veterán

-

Petykemano

veterán

Nem érzem azt, hogy egyik vagy másik cég termékei jobban célpontja lenne ilyen kutatásnak, tehát nem sejtek részrehajlást. Olyan mintha általában ez a kérdés kevesebb nyilvánosságot, vagy kevesebb kutatást kapott volna a Zen előtt.

Persze nem kizárt, hogy arról van szó, hogy a cégek egymás lejáratása érdekében keresztfinanszírozzák egymás biztonsági réseinek felderítését, amit a Zen óta tudnak vagy érdemes megtenni.Találgatunk, aztán majd úgyis kiderül..

-

Petykemano

veterán

Zen5, Zen 5, CPUz, CPU-z, hwinfo, AMD eng sample

Hybrid 12-core config of AMD Ryzen 8000 “Strix Point” APU seemingly confirmed by leaked screenshots

Eredeti forrás: [link]

L1$:

- 4x32 + 4x48

- 8x32 + 8x48Amennyiben a képernyőkép valid, az igazolja a 48Kb-os L1d-re vonatkozó pletykákat.

Zen4 esetén az még 8way, itt már 12wayAmi még nagyon különös az az L2$!

8 magra 2x1M?

Hmm... nem, nem hiszem, hogy az AMD a normál és dense magok között változtatna a cache hierachián - legfeljebb az L3$ méretén. Gyanítom, hogy ez a HWinfo hibája, ami E magnak ismeri fel és az Intel E magjai esetében tényleg úgy van, hogy 4 magos clusterek vannak 1db L2$-re fűzve és csak rosszul ismeri fel.És míg a Zen4 esetén az L2$ is 8 way, addig itt már 16 way.

Azt gondolom, hogy a Zen4 esetén a L2$ méretének növelése valóban csupán azt a célt szolgálhatta, hogy elférjenek benne az AVX512-höz használatos nagyobb hosszúságú adatok és alig járt IPC növekedéssel. Addig az asszociativitás növelése viszont valóban hozzájárulhat ahhoz..A zen4-hez CPUz (CPU-z) 2022 szeptemberben jelent meg [link] De akkor már nem AMD Eng Sample volt a megnevezése.

Zen4-ről nem feltétlenül CPUz, vagy hwinfo jellegű leak pedig január és május között jelent meg. Vagyis 4-8 hónappal a szeptemberi release előtt.Bennem ez azt erősíti, hogy a 2024Q1-es Zen5 rajt sínen van.

[ Szerkesztve ]

Találgatunk, aztán majd úgyis kiderül..

Új hozzászólás Aktív témák

- LEGO klub

- USB to S/PDif konverter a modern RIAA, elektroncsövekkel

- Motorola Edge 40 - jó bőr

- Eredeti játékok OFF topik

- Kerékpárosok, bringások ide!

- Revolut

- Politika

- antikomcsi: Való Világ: A piszkos 12 - VV12 - Való Világ 12

- Nyaralás topik

- Intel Core i5 / i7 / i9 "Alder Lake-Raptor Lake/Refresh" (LGA1700)

- További aktív témák...

- Suzuki Swift 2005 1.3 GLX CD AC - AndroidAuto & CarPlay

- Bomba ár! HP Elite X2 1011 G1 - m5 I 8GB I 256GB SSD I 11,6" FHD Touch I CAM I W10 I Gari

- Bomba ár! Lenovo ThinkPad T490 - i5-8GEN I 8GB I 256GB SSD I 14" FHD I Cam I W10 I Garancia!

- 8db GeForce RTX 3090 Egyben

- VAST AI - VAST AI - VAST AI - GeForce RTX 3090

Állásajánlatok

Cég: Alpha Laptopszerviz Kft.

Város: Pécs

Cég: Ozeki Kft.

Város: Debrecen