Új hozzászólás Aktív témák

-

S_x96x_S

őstag

Ez az a GPU-s Infinity Cache és Smart Access érdekes lesz.

főleg, hogyha adatbázis programok is elkezdik használni gyorsításra ..

Egyre inkább heterogén rendszerek lesznek.Ami még érdekes lehet, hogy ezáltal

az AVX-512 -es utasítások végrehajtását ( a jövőben ) simán át lehet tolni a GPU-ra.

vagyis nem lesz annyira sürgős az AVX-512 implementálása.

Mottó: "A verseny jó!"

-

S_x96x_S

őstag

válasz

S_x96x_S

#4251

üzenetére

S_x96x_S

#4251

üzenetére

igazából a PCIe5.0 - el minden megváltozik ..

dupla sebesség + CXL támogatás lehetősége,

de addig is .. erősödhet az AMD ...STH: https://www.servethehome.com/amd-radeon-rx-6900-xt-6800-xt-6800-rdna-2/

"It will be interesting to dive more into what this is. We know AMD needs a cache coherent interconnect for its exascale efforts and effectively had to swap CCIX for CXL. It would be very interesting if this is an early derivative of this effort."Mottó: "A verseny jó!"

-

Mahrenburg

senior tag

válasz

S_x96x_S

#4250

üzenetére

S_x96x_S

#4250

üzenetére

"Sokan bütykölnek X86-ot... " - Én is próbálgattam otthon, de egyelőre nem sok sikerrel...

"Egy fel nem használt Phenom II matrica olyan mint egy nap ami sosem kelt fel, egy múló szerelemről szóló dal amit sosem énekeltek, egy harcos szív amely sosem dobbanhatott..!" by Habugi

-

Petykemano

veterán

válasz

S_x96x_S

#4251

üzenetére

S_x96x_S

#4251

üzenetére

Hmm

Smart.Access ide vagy oda, a fusion lényege az volna, hogy nem csak közös címtérben dolgoznak, hanem tényleg közös memóriát használnak és se pcie-n keresztül, ad absurdum se memóriában nem kell másolgatni a feldolgozandó adatot."Full Access to gpu memory"

Arra utal, hogy a CPU úgy fogja látni a gpu memóriáját, mintha egy másik memory pool lenne.A sebességnövekedés.ott érhető tetten, hogy a gpunak alacsonyabb késleltetéssel fognak rendelkezésére állni az adatok, amiket a CPU feldolgozás/előkészítés után máskülönben a rendszermemóriában tárolna.

Szóval ez arra jó, hogy ha valami alapvetően a gpun fut, akkor annak alá tud dolgozni a CPU. Ez a CDNA esetében is szerintem kifejezetten hasznos lesz

Sőt, bármihez jó, ami valami gyorsítón.fut, akár gpu, akár fpga.De azt nem látom.ebbe bele, hogy ezzel megvalósítható lenne az AVX512 utasítások offloadolása.

De az irány persze mindenképp a heterogén feldolgozás, és azt értem, hogy ezzel egy programban meg lehet majd mondani, hogy egy parancs egy adathalmazon min fusson (vagy akár adattípustól függően automatizálni is lehet) csak én még azt nem értem, hogy egy-egy utasítást kiszervezése lehetséges-e egyáltalán.

Találgatunk, aztán majd úgyis kiderül..

-

Cathulhu

addikt

válasz

S_x96x_S

#4251

üzenetére

S_x96x_S

#4251

üzenetére

elvileg a one API lenyege pont az lenne, hogy ugymond sebessegvesztes nelkul kapsz egy absztrakciot az osszes ilyen vektor kod felett, mint AVX, OpenCl, etc, vagy nem jol ertem? Mert akkor meg pont az intel dolgozik ezen.

Amugy ez csak most ugrott be, de mi van ha mondjuk Zen5-os Epycekben lesz egy programozhato FPGA resz, ahova a vevo olyan vektorgyorsitot tolt fel amilyet csak akar. Pl kijott egy uj AVX utasitaskeszlet? Vagy egy uj AI utasitas? Nopara, frissitsuk anelkul, hogy ki kellene dobni. Vagy ezt a reszt mar erosen tulgondolom?Ashy Slashy, hatchet and saw, Takes your head and skins you raw, Ashy Slashy, heaven and hell, Cuts out your tongue so you can't yell

-

yagami01

aktív tag

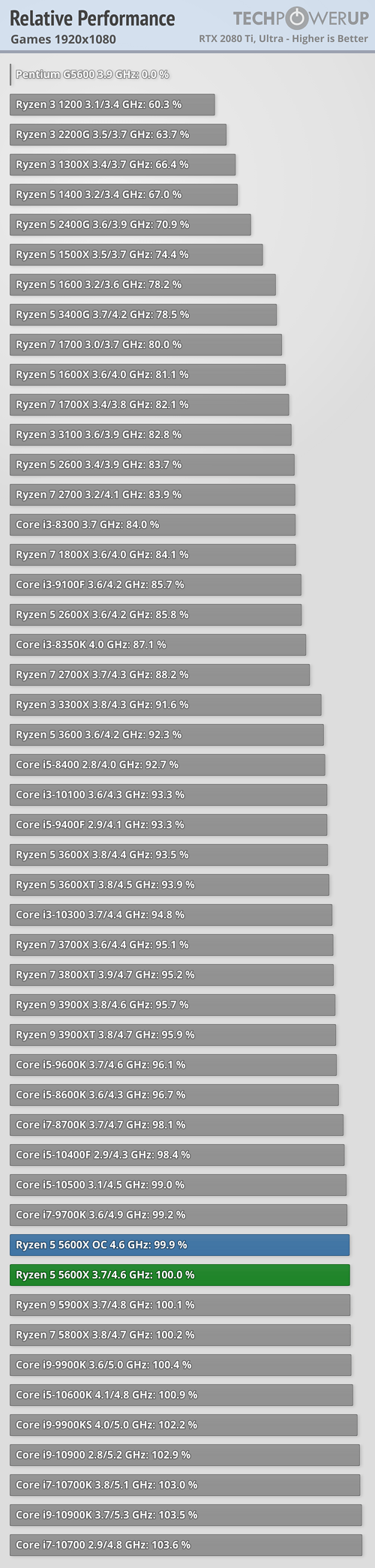

Ezt a képet ide is berakom.

-

hokuszpk

nagyúr

egy irastudo versenytarsfigyelo kérem elemezze ezt :

[ Szerkesztve ]

Első AMD-m - a 65-ös - a seregben volt...

-

Sirpi

senior tag

válasz

hokuszpk

#4258

üzenetére

hokuszpk

#4258

üzenetére

Röviden:

Feltörték azt a titkosítást, ami az Intel procik firmware upgrade-jét védi.

Ezáltal vissza tudják fejteni a javításokat, és rájöhetnek, miket javított, ami alapján a patch-eletlen procik támadhatók. Sőt, hackerek akár kiadhatnak saját "javításokat", amikkel nem kívánt dolgokat tudnak a procik kódjába csempészni.

Nehéz felmérni, hogy ez mekkora problémát okozhat, mivel ez az első alkalom, hogy Intel-féle procititkosítást sikerült feltörni.Hazudnék, ha cáfolnám annak tagadását, hogy ez az ital nem nélkülözi a koffeinmentesség megnemlétének hiányát. Na most akkor van benne koffein, vagy nincs?!

-

-

Maelephant

aktív tag

Azért a scope nem akkora, mint amilyen szenzációs hírként lehozták ezt:

The key can be extracted for any chip—be it a Celeron, Pentium, or Atom—that’s based on Intel’s Goldmont architecture. -

Petykemano

veterán

Sisoft

5600X

"Overall the 6-core Zen3 is only about 16% faster than the old Zen2, as it can cannot rely on much faster Turbo as we’ve seen with its other siblings. While we may have hoped for more, the XT Zen2 have too good performance rather than Zen3 not improving enough."Executive Summary: Zen3 (6-core) is ~15-40% faster than Zen2 across all kinds of algorithms. Thus we’ll give it 9/10.

5800x

"We previously saw Zen2 40% faster than Zen+ and now Zen3 is a similar 40% faster than Zen2: in effect for the same number of cores (8C/16T), Zen3 is 2x faster than Zen+! Simply astonishing!""Executive Summary: Zen3 is ~25-40% faster than Zen2 across all kinds of algorithms. No choice but give it 10/10 overall!"

[ Szerkesztve ]

Találgatunk, aztán majd úgyis kiderül..

-

Maelephant

aktív tag

válasz

Petykemano

#4263

üzenetére

Petykemano

#4263

üzenetére

Hát ez elég erősen hangzik, ez bizony nem kis növekmény

-

awexco

őstag

válasz

Petykemano

#4263

üzenetére

Petykemano

#4263

üzenetére

Érdekes , h a 7900x menyivel jobb eredményeket tol mint a 9900k ...

I5-6600K + rx5700xt + LG 24GM77

-

Danex

addikt

Ki hol tervez/vár procira?

azt lehet tudni, hogy nov5 szemmel látható érték mennyiség lesz-e?

azt lehet tudni, hogy nov5 szemmel látható érték mennyiség lesz-e? -

BiP

nagyúr

válasz

qwe8585

#4269

üzenetére

qwe8585

#4269

üzenetére

Annyira nem rohanok, csak kb. február márciusra szoktak leesni a karácsonyi láz miatt feltolt árak. Azért gondoltam, hogy akkor majd körbenézek, mit érdemes. (meg januárra ígérik úgyis a friss BIOSokat a B450-es lapokhoz, szóval azt fizikai okokból mindenképp meg kéne várni)

Intelre felesleges várni szerintem. Bár a Rocket Lake-nél 2számjegyű IPC növekedést ígérnek az új Cypress Cove alapú magok miatt, ami Intelnél nagy szó, viszont nem hiszem, hogy árversenyre tudnának kelni, pedig nem lesz olcsó a Zen3 sem.[ Szerkesztve ]

-

Petykemano

veterán

A navi21-ben bemutatkozott infinity cache, ami ahogy a képen látható, egyrészt körülöleli a lapkát, másrészt az IF és a Memória vezérlő között helyezkedik el.

Navi21:

128 MB Infinity Cache = ~86.6 mm² = 1.48 MB/mm²

zen2 CCD:

32 MB L3$ = ~33.4 mm² = 0.96 MB/mm²Mi a valószerűsége/valószínűsége annak, hogy ez megjelenjen ha máshol nem is, de az EPYC IO lapkáján?

Mondjuk ha az IO lapkát 7nm-en gyártanák akkor 256MB infinity cache-sel a fedélzeten talán még mindig elférnének 450mm2-ben, nem?

Találgatunk, aztán majd úgyis kiderül..

-

Inkább csak matematikai hiba, látszik is abból, hogy 1 negyedév alatt annyit nőtt az overall, mint kb a többi 4 negyedév alatt. Jó lenne, ha belinkelték volna az AMD-s forrást, így nehéz kinyomozni hol a hiba.Nézem a tomiék cikkjét, ez a tábla érdekes, az a kérdés, hogy mi a nem client.

Amúgy mik azok a kérdőjelek? Nincs bázisadat vagy wtf?

[ Szerkesztve ]

solfilo

-

Busterftw

veterán

Hat a cikkben az irjak, hogy "AMD shared the recent Mercury Research CPU market share results" szoval nem hiszem, hogy kamuznanak.

A cikk szerint AMD pl a press kommunikaciobol kihagyta a szerver adatokat.

Ezek szerint az AMD is erre alapoz. -

Cathulhu

addikt

válasz

Busterftw

#4277

üzenetére

Busterftw

#4277

üzenetére

ott valami workarounddal meghekkelte azt a kijelenteset es mar az elozo negyedevben is azt mondta megvan a 10% ahogy terveztek. Talalt valami kiskaput a szovegertelmezesben.*

Amugy szerintem kapacitas. Tekintve, hogy az intel rekord negyedeveket jelent szerver fronton, valoszinuleg jobban bovul az a piac mint gondoltak. Es ugye most van epp a konzol hajtas, azt meg le kell gyartani, megha az epyc zsirosabb falat is lenne. Sajat CPU-kkal GPU-kkal ugye ugy jatszanak ahogy akarnak, de ugyanezt a Sony es MS altal rendeltekkel nem tehetik meg.

*ezt mondta: "We accelerated our server and mobile processor businesses significantly in the second quarter, resulting in Ryzen and EPYC processor revenue more than doubling year-over-year. Importantly, we met our double-digit server processor market share goal as data center products accounted for more than 20 percent of our second quarter revenue."

Ezt mindenki ugy ertelmezi ahogy tudja/akarja, az en olvasatomban azt jelenti, hogy raduplaztak a szerver eladasokra es ezt a duplazast extrapolaltak market share-re es igy kijott a duplaszamjegy. Csak az nincs benne, hogy kozben a market maga jelentosen nott, igy a dupla eladas onmagaban nem volt egyenlo dupla share-rel[ Szerkesztve ]

Ashy Slashy, hatchet and saw, Takes your head and skins you raw, Ashy Slashy, heaven and hell, Cuts out your tongue so you can't yell

-

Petykemano

veterán

Találgatunk, aztán majd úgyis kiderül..

-

sNk77

aktív tag

válasz

Petykemano

#4281

üzenetére

Petykemano

#4281

üzenetére

Ez alapján nekem az 5600X bőven elég lesz játékra, ideje távoznia a 6700k-nak

. Még kiváncsi vagyok 5600X vs 10600k-ra azért, mert a 10600k meg olcsóbb.

. Még kiváncsi vagyok 5600X vs 10600k-ra azért, mert a 10600k meg olcsóbb.nádpálca

-

BiP

nagyúr

-

sNk77

aktív tag

Aha valahogy én is így számoltam, vagyis csak ránéztem, hogy 300 dollár az 5600X ami biztos nem áll meg a 10600K 90k-s árában. Meg a TDP se utolsó, 10600K 125W, 3600X 95W, 5600X 65W. Most, hogy mondtad a 3600X-et még az is lehet jó lenne, kiváncsi vagyok a 3600X vs 5600X-re is. És eszembe jutott, hogy én AMD kártyát szeretnék majd, akkor meg már illene mellé ryzen a SAM miatt. Kivárom annak a tesztjeit is.

nádpálca

-

BiP

nagyúr

Ami méginkább az AMD felé billenti a mérleget, mert az AMD számolása közelebb áll a valós, átlag felhasználáshoz.

#4284 sNk77 : +19% IPC-t mondanak, és erre még rájön pár % órajel emelkedés is. Szóval jóval gyorsabb lesz.

az 5000-es ryzenekkel szemben az intel egyetlen fegyvere már csak az ár maradt, a gaming is kiesett, mindenben alulmaradt.

Új versenyt majd a Rocket Lake hozhat 2021Q1 után (ha nem csúszik), aminél kétszámjegyű IPC növekedést jósol az intel, amivel közelebb kerülhet a Zen3-hoz.[ Szerkesztve ]

-

HSM

félisten

"Ami méginkább az AMD felé billenti a mérleget"

Éppen fordítva gondolom.

Lásd: [link] és [link] .A 10600K az 56 másodperces turbó időablakán belül átlagosan nem mehet 125W valós fogyasztás fölé, ha a gyári specifikáció szerint van beállítva a BIOS. Míg pl. a túloldal 65W TDP-s 3600-asának 88W a "valós fogyasztás" limitje tartósan, tehát inkább a 95W-os TDP-s Intelekhez áll közelebb.

[ Szerkesztve ]

-

wwenigma

Jómunkásember

"ha a gyári specifikáció szerint van beállítva a BIOS"

Alapertelmezetten a lapok tobbsegen intelnél alapertelmezetten ki van kapcsolva a tiltas. Alapertelmezetten.

Ha pedig a fogyasztással kevered a TDP-t akkor szolok hogy a CPU core TDP az annyi amennyit mondanak. A SOC fogyasztását ne add hozzá.

[ Szerkesztve ]

Steam: http://bit.ly/1rRuf8p , Origin: wwenigma -- | -- Jiayu F1 / G3C / OT995 cuccok: http://bit.ly/1w44CI2 -- | -- ZTE V5 Red Bull -> http://bit.ly/1mgtfrd -- | -- Xiaomi RN3SE -> http://bit.ly/2r8DlV7 -- | -- Live Stream: twitch.tv/wwenigma

-

Petykemano

veterán

Zen4 találgatások:

"I expect that Zen4 is very similar project to Zen2. It will widen the FP and L/S by 2x, add (most likely) 2x the cores per chiplet. I hope that AMD will go Zen3 route with regards to CCX and share a huge pool of (64MB?) L3 cache among 16 Zen4 cores. Similarly to Zen2, I think they will aim at around 15ish% IPC jump versus Zen3 - this would leave Zen5 with very optimistic (but obviously achievable) target of ~21% IPC improvement coming from Zen4, if they were to keep the 40% increases between their "tocks" (EX->Zen1; Zen1->Zen3 ; Zen3->Zen5?).

There are some rumors of further chiplet design evolution and some possible massive (L4?) caches, new memory controller + DDR5 support, shrinking of the IOD etc. Zen4 definitely looks like the next big core count increase and a major platform update."

[link]

"It will get difficult to scale the cache size larger without increasing latency. Some form of L4 may be more likely. I don't think they are going to jump to a 16 core CCX right after going to an 8 core. It may be possible that they would make a 16-core chiplet with 2 CCX on one die. I expect Zen 4 to be very similar to Zen3. Zen 3 is a new architecture, so I don't think we will see huge changes to most of the functionality. Using stacked chips allows for much higher bandwidth, so I wouldn't be surprised to see internal pathways widened significantly and much increased FP performance. Stacked chips can easily use 1024 bit links; a single HBM stack is 1024-bits, so I am wondering if internal paths will actually go up to 1024 bits to match."

[link]

"Here is some speculation. Due to recent AMD's graphics reveal and infinity cache, and that zen arch was inspiration for it, I think that zen4 could have L4 cache.

So CCD would have two octacore CCXes, each having its own 32MB L3 cache, both connected to CCD wide 64 MB L4 cache.

This way you get to reuse zen3 topology, but also save on latency. Also, cache, or to be more precise, SRAM is getting "cheaper" on smaller nodes.

I am not EE, so this could be nonsense, but thought it could sprout some discussion."

[link]

Az FP teljesítmény növeléssel egyetértek. Logikus volna, ha megint dupláznának és ezzel megérkezne az AVX512 támogatás is.

Azzal is egyetértek, hogy logikus lenne, ha 5nm-en duplázódna az egy CCD-ben elhelyezett magok száma. Viszont ezt egyelőre csak úgy tudom elképzelni, hogy 2 CCX kerül megint 1 CCD-be.A megvalósítás viszont kérdéses. Az eléggé tradícionális lenne, ha tényleg hagyományos módon csak simán bekerülne 2 8magos CCX 1 CCD-be, pont úgy, ahogy a zen1-2-nél volt. Miért csinálnának ilyet? Miért tennék egybe? Túl kicsi lenne 1 CCX-szel a lapka?

Másrészről ott vannak az advanced 3d tokozások.Én L4$ vonatkozásában hasznosabbnak gondolnám, hogy ha nem 2 8magos CCX-et kötne össze, hanem ha az IOD-ra kerülne és az összes CCX-et összekötné. Persze az elég nagy helyet igényelne. Pl: 128MB-os Infinity Cache 7nm-en 86mm2 lenne.

Pl desktop esetén a jelenlegi 12nm-en készülő Matisse IOD 125mm2. Ha ezt a zen4 esetében levinnék 7nm-re, akkor biztos csökkenhetne a mérete mondjuk 80-90mm-re (nem számolva persze azzal a lehetőséggel, hogy a DDR5 és PCIe5-nek milyen helyigénye van) ha ehhez hozzátennénk még a 128MB-os oo$-t akkor egy 160mm2-es IOD jönne ki. Ezzel ha a zen4 esetén továbbra is 8 magos CCX-eket 32MB L3$ köt össze, akkor kezelni lehetne 4CCX-et is.Ami a találgatásból fájóan hiányzik nekem az a Warhol.

Ami ugye még mindig zen3. És nem tudjuk a célját. Már a múltkor is pedzegettem azt kérdést, hogy a oo$-nek lehet-e köze a Warholhoz.Egy olyan lehetőséget például elképzelhetőnek tartok, hogy a Warhol egy olyan fejlesztés, aminek az IOD-ja már 7nm-en készül és rendelkezik mondjuk 64MB oo$-sel (ezzel nagyjából méretkompatibilis maradna a Matisse IOD-jal) és továbbra is ki tudná szolgálni az alapvetően zen3-as CCD-ket. (zen3+?)

Találgatunk, aztán majd úgyis kiderül..

-

Yutani

nagyúr

Vajon mikor száll fel ma az NDA, mikor kerülhetnek ki a tesztek a Ryzen 5000 sorozatról?

#tarcsad

-

HSM

félisten

válasz

wwenigma

#4288

üzenetére

wwenigma

#4288

üzenetére

"Alapertelmezetten."

Intelnél a lap gyártójára van bízva, milyen limitet lát jónak az adott terméknél. Pár kattintás a BIOS-ban egyébként módosítani, ha valakinek nem tetszik, amit a lapgyártó kitalált, a gyári pontos paraméterek is ismertek."fogyasztással kevered a TDP-t"

Nincs keverés, csupán jeleztem, hogy míg Intelnél a dobozra írt TDP egyezik a a termék gyári paraméterek melletti időablakon belüli maximális átlagfogyasztásával (memóriavezérlővel, IGP-vel mindennel együtt), addig AMD-n ez tipikusan egy magasabb érték.

Két CPU valós fogyasztásának összehasonlítása csak akkor korrekt, ha a teljes CPU-t (tehát a SoC-ot is beleértve) vannak összehasonlítva. A TDP nézegetésének pedig a lényege igazából ez kellene legyen, hogy a vásárló milyen fogyasztással és hűtéssel kell számoljon. -

wwenigma

Jómunkásember

Gondolom a lap gyártója kesziti a biosokat amikben meg van adva az alapertelmezett beallitas. Ne nézz már madárnak....ugyanakkor pedig megnézném hogy mi is all kozelebb a valósághoz ha kikapcsolt limitekkel futnak. Alapertelmezetten.

A TDP pedig nincs kőbevésve és legfőképpen nem fogyasztást ad meg W-ban hanem a hűtésre vonatkozik. Ez az amit fentebb is írtak neked. Ennyi erővel AMD esetén add hozzá még az aktualis datumot is hogy csunyabbnak tűnjön. Mint a pincér a számlához, mert az idő pénz.

[ Szerkesztve ]

Steam: http://bit.ly/1rRuf8p , Origin: wwenigma -- | -- Jiayu F1 / G3C / OT995 cuccok: http://bit.ly/1w44CI2 -- | -- ZTE V5 Red Bull -> http://bit.ly/1mgtfrd -- | -- Xiaomi RN3SE -> http://bit.ly/2r8DlV7 -- | -- Live Stream: twitch.tv/wwenigma

-

HSM

félisten

válasz

wwenigma

#4292

üzenetére

wwenigma

#4292

üzenetére

Megpróbálom még egyszerűbben leírni, hátha úgy megérted....

Úgy van értelme összehasonlítani adott termékek (CPU) fogyasztását, ha abban minden benne van, ami annak működése során áramot fogyaszt, tehát a SoC is. AMD-n is csak azt számoltam bele, amit a másik oldalon is. Mindkét CPU esetén a gyártó által ajánlott működési paraméterek mellett.

AMD-nél valóban nem fogyasztást ad meg (erről írtam

), Intelnél viszont igen [link] .

), Intelnél viszont igen [link] . -

Yutani

nagyúr

Why Intel Processors Draw More Power Than Expected: TDP and Turbo Explained

AMD Ryzen TDP Explained: Deep-Dive on TDP Definitions & What Cooler Manufacturers Think

Mindkettőtöknek, szeretettel. Én nem olvastam el őket.

[ Szerkesztve ]

#tarcsad

-

HSM

félisten

Köszönöm, mindkét irományt jól ismerem.

Úgy tűnik, kötekedő fórumtársunkkal ellentétben.

Úgy tűnik, kötekedő fórumtársunkkal ellentétben.A kedvenc idézetem az egyikből: "Our opinion is this: the AMD TDP formula takes three individually useful numbers and blends them all together into one un-useful number that can’t be reverse engineered back into its original parts. It’s like summarizing someone’s personality by adding their birth date and the number of letters in their last name together. AMD did provide tCase, tAmbient, and HSF θca to us upon request, but those aren’t the numbers that get printed on the box."

Intelen persze nem ideális, hogy a lapgyártók azt állítanak be, amit akarnak limitnek, de legalább így nincsenek motiválva "alternatív" megoldások keresésébe, mint pl. a CPU telemetriai adataival való trükközés a piros CPU-k esetén.

-

yagami01

aktív tag

válasz

Petykemano

#4289

üzenetére

Petykemano

#4289

üzenetére

Igen, én is hiányoltam a Zen3+ -t (az lenne elv. a Warhol, vagy valami olyasmi, ha jól emlékszem, tehát elv. még jönnie kéne még egy gennek ebbe a tokozásba). Az lehetséges, hogy ebből mégsem lesz semmi és előbbre hozzák a DDR5 támogatást meg a mindent? Ha viszont lenne, akkor a 15% már nem 15% lenne a Zen3+ -hoz képest, mert ugye azt csak a 3-hoz képest írja. SMT4-et sem láttam, de lehet ott van a sorok között? Csak én nem értek hozzá annyira, hogy kitudjam olvasni. (: És akkor ha jól értem a 4-el nőnek megint a magszámok, nem tudom ez duplázást jelentene-e, lenne-e annak értelme, lehet nem...

-

Petykemano

veterán

válasz

yagami01

#4297

üzenetére

yagami01

#4297

üzenetére

A Warhol egy kakukk tojás.

Én egyaránt elképzelhetőnek - ám merésznek - tartom azt, hogy a Warhol egy filler a Vermeer és a Raphael között, ami az IOD-on javít, cserébe mondjuk valamivel hamarabb jön a szokásos 14-15 hónapos ciklusnál. Hasonlót láttunk már: zen+. A zen és zen2 közözz ugye több idő telt el.

Ha ez így lenne, akkor elképzelhető, hogy a Warhol még mindig AM4-be érkezzen.De azt is elképzelhetőnek tartom, hogy a Warhol már AM5 lesz és a Ryzen 6000 felső szintjét töltik csak fel zen4-gyel, az alsó szint zen3-as Warhol. Ha nem lennének pletykák arról, hogy a az 5000-es szériában egyaránt lesz Renoir és Cezanne, akkor persze ezt a lehetőséget elképzelhetetlennek tartanám. De így...

Nincs szó SMT4-ről.

Szerintem 4-gyel nem tudják növelni a magszámot. 8 magos most egy CCX. Ezt valószínűleg egy pár évig megint nem piszkálják. Az a kérdés, hogy a zen4-es CCD-be 1 8 magos CCX kerül, vagy 2, vagy bevetnek valamilyen speciális 3d tokozást .

Találgatunk, aztán majd úgyis kiderül..

-

yagami01

aktív tag

válasz

Petykemano

#4298

üzenetére

Petykemano

#4298

üzenetére

Új hozzászólás Aktív témák

Állásajánlatok

Cég: Promenade Publishing House Kft.

Város: Budapest

Cég: Ozeki Kft.

Város: Debrecen

azt lehet tudni, hogy nov5 szemmel látható érték mennyiség lesz-e?

azt lehet tudni, hogy nov5 szemmel látható érték mennyiség lesz-e?

. Még kiváncsi vagyok 5600X vs 10600k-ra azért, mert a 10600k meg olcsóbb.

. Még kiváncsi vagyok 5600X vs 10600k-ra azért, mert a 10600k meg olcsóbb.

), Intelnél viszont igen

), Intelnél viszont igen